회로기초05

[ADC]

Analog to Digital converter의 약자. 즉 연속적인 analog 신호를 0과 1로 discrete하게 구성된 digital 신호로 변환하는 칩(I/C)이다.

ADC 변환과정

1.필터링 -아날로그 신호의 노이즈들을 제거, 필터링에는 LP(LowPass)나 HP가 있을수 있다.

-

샘플링[표본화] -샤논의 표본화 정리에 따른 표본값을 추출-> 복원가능한 정도의 신호만을 이산하는 과정 표본화는 원 신호를 시간축 상에서 일정한 주기로 표본값을 추출하는 것을 의미. 이렇게 추출된 펄스열을 플스 진폭 변조(PAM, Pulse amplitude Modulation)이라함.

-

양자화 -샘플링에서 얻은 pam신호를 유한한 수의 진폭값을 가장 가까운 값으로 근사화 하는 과정. 진폭축에 따라 이산값으로 변환

-

부호화 양자화된 신호 전송시에 잡음에 민감하므로 전송및 처리에 적합하도록 부호화

[ADC방식의 종류]

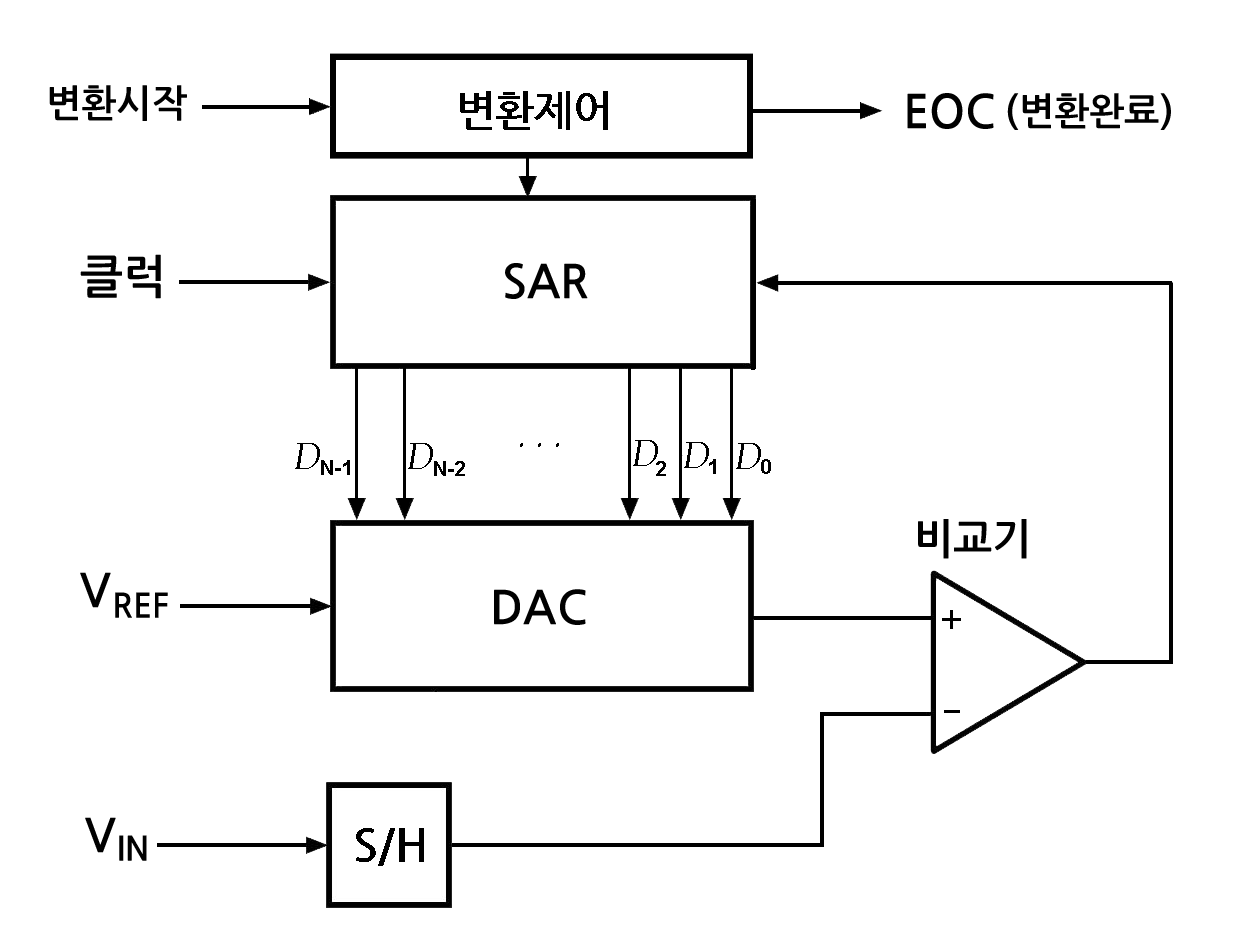

1.SAR ADC(Successive Approximation ADC - 축차 비교형)

장점 : 구조가 간단. 정확도가 다른 ADC에 비해 정확 단점 : 샘플링 속도가 느리고, 비교기의 숫자가 늘어날 수록 비용 부담이 커짐.

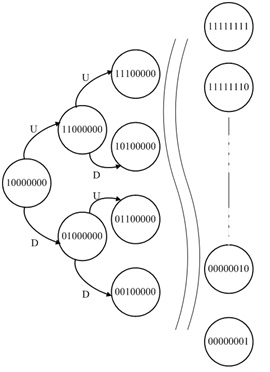

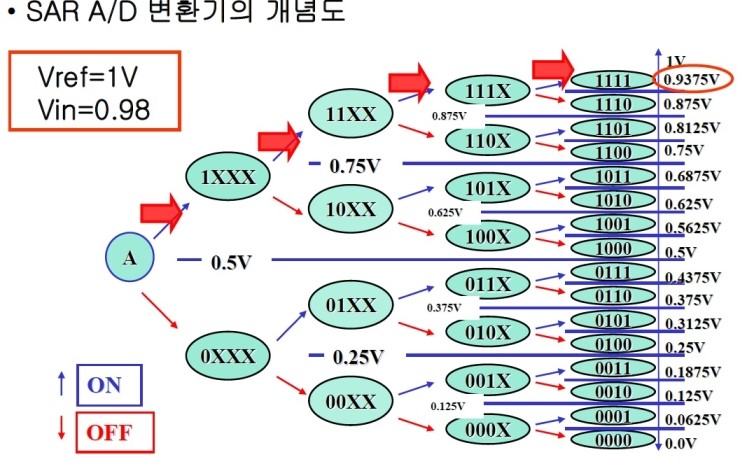

우선 SAR의 최상이 비트를 0으로 설정하고 나머지를 1로 설정. SAR의 초기값 = 01111111(또는 10000000) => DAC => VDAC는 VREF/2 근처.

만약 DAC 전압보다 입력 전압이 작다면 VREF의 반 이하가 됨. 즉 DAC로 변환된 아날로그 전압이 입력전압과 비교하여 작다변 비교기의 출력이 logic ‘1’로 출력이 되고, 출력값을 보고 SAR의 최상이 비트를 0으로 설정.

변환 방식

(1) 레지스터 또는 아날로그 전압으로 변환 시작에 대한 신호가 전달된다.

(2) 제어회로는 MSB부터 변환을 시작한다.

(3) SAR의 초기값은 최상위 비트는 0, 나머지 비트는 1 이다. (sAR = 0111111…11111)

(4) 설정된 분해능 (샘플링 율) 에 따라 DAC는 digital을 analog 전압으로 변환하고, 이를 Vin과 비교한다.

* DAC 전압보다 Vin이 작으면 (Vin < Vref/2) 최상위 비트를 0으로, Vin이 크면 (Vin > Vref/2) 최상위 비트를 1로 설정한다.

* 위 변환은 한 클럭동안 이뤄진다. (클럭의 주기 > DAC 변환시간 + 비교기 전파시간 + SAR논리회로 전파시간 + DELAY)

(5) 최상위 비트가 결정되면, 그 다음 비트를 결정해나간다.

(6) 전체 비트 수 만큼 클럭을 진행하면 모든 비트 결정이 완료된다.

(7) 변환이 끝나면 EOC 신호를 설정하여 외부에 변환완료를 알려주며 마무리한다.

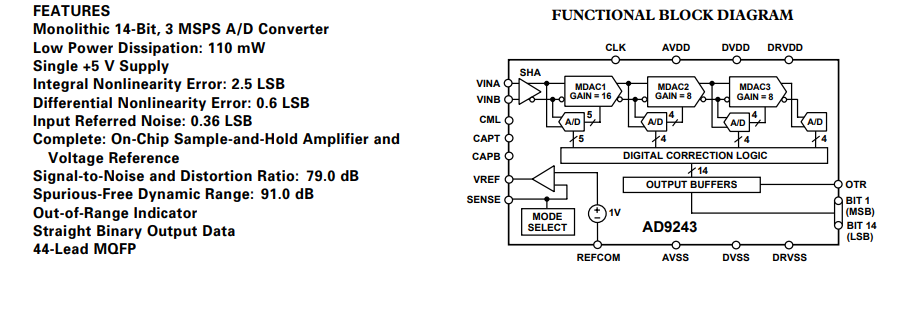

[AD9243]

병령 방식 14비트 컨버터. 샘플링 속도가 3.0msps 라서 클럭 속도는 3.0m 보다 작아야한다. 5v공급 전원이 필요하고. 에러율은 아래 2비트 정도는 에러 율이 있을수 있다.

예)입력 전압이 2.5v가 들어오고 기준전압이 5v일경우 (2.55) 16384(14비트, 2의 14승) = 8192

8192는 2진수로 번해서 14비트로 보면 = 10 0000 0000 0000로 변환되어서 출력 된다 보면 된다. 이걸 역으로 계산해서 확인한다.

그래서 AD9243은 아날로그 전압이 들어보면 14비트로 변환해서 확인할 수 있다.

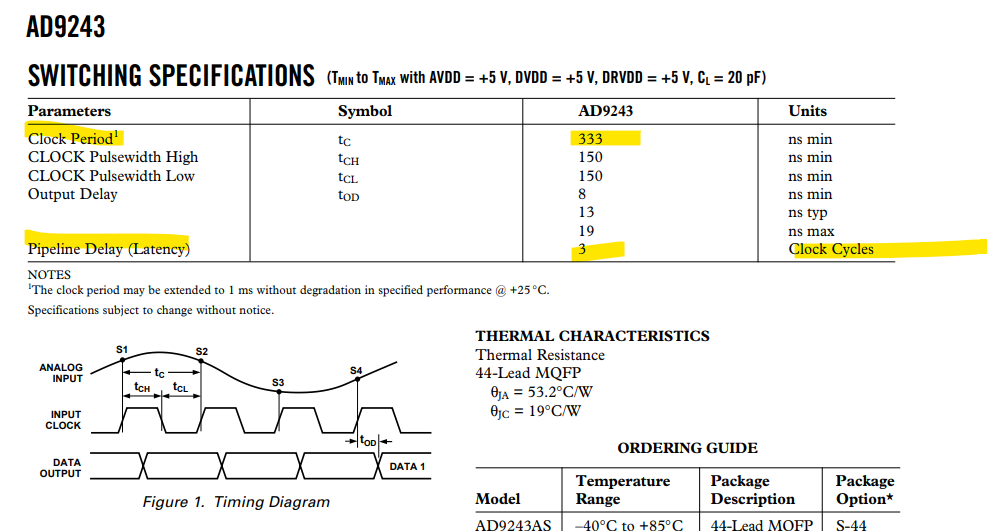

클락 주기는 333나노 정도이고 파이프라인 딜레이는 3나노 정도이다. 타이밍 다이어그램을 보면 입력이 들어왔을때 3클락 뒤에 데이터를 읽을 수 있다. S1이 들어오면 S4에 읽을 수 있다.

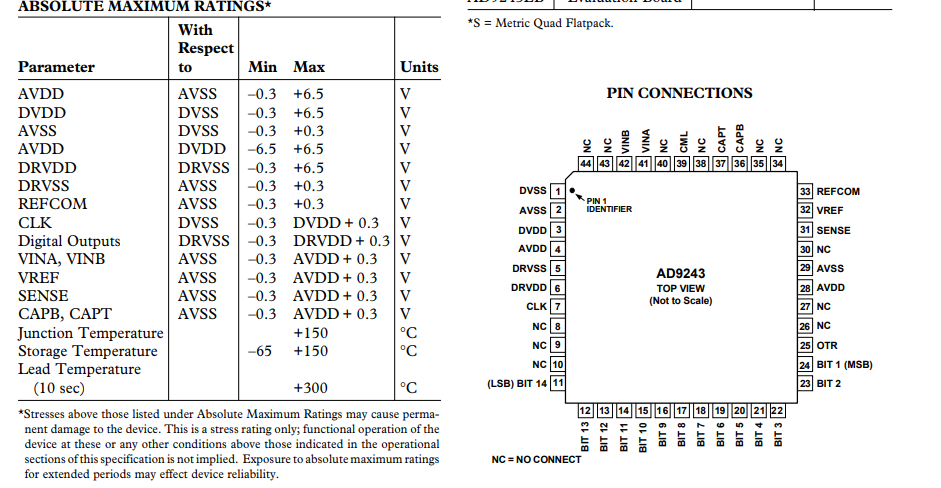

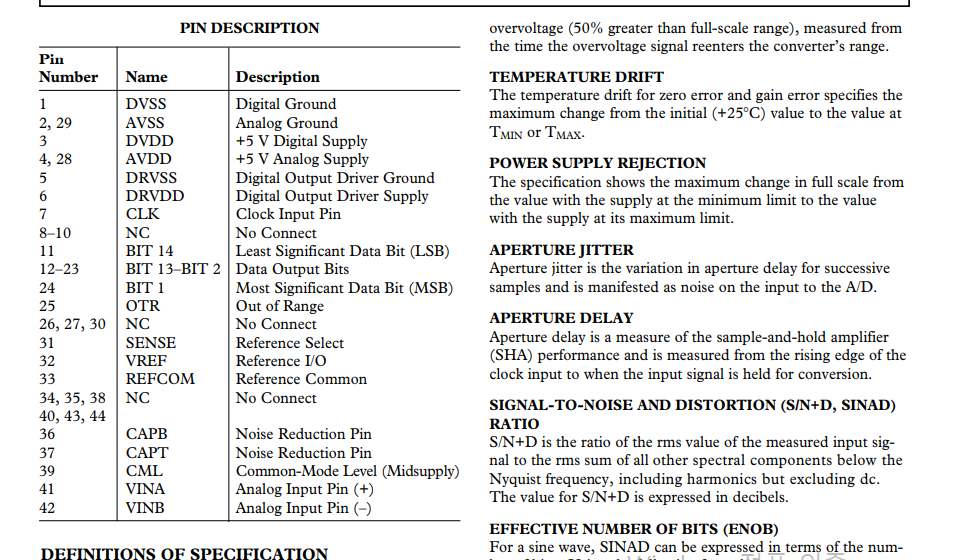

핀아웃 구성. 7번이 클럭 인풋 핀이고, 클락은 3M보다 낮게 줘야 한다.

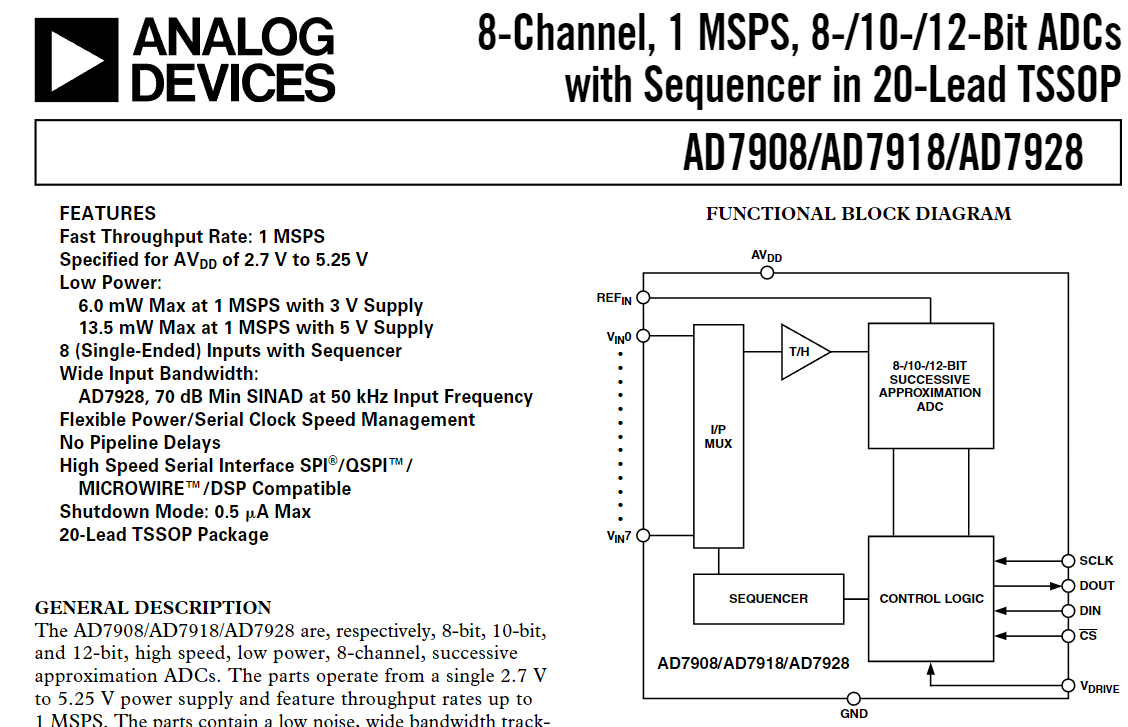

[AD7908]

12비트와 8개의 아날로그 신호. 속도는 1MPS FPGA나 MCU단에서 조절을 해야 한다.

크기에 배해서 8채널을 받을수 있어 좋다.

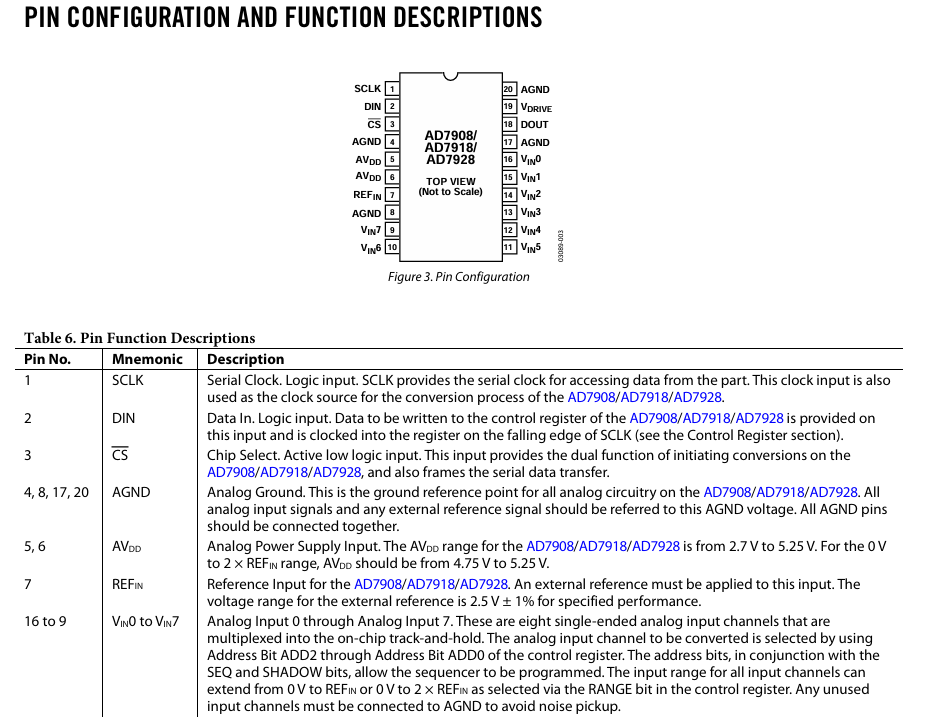

1: 칩의 속도를 지정해줄 클락 입력 2: 컨트롤 레지스터 사용 3: 칩샐렉, 제어를 해줘야 한다 5,6: 0~5V까지 범위 7: 레퍼런스 전압 설정 18 : 데이터 받는 부분.

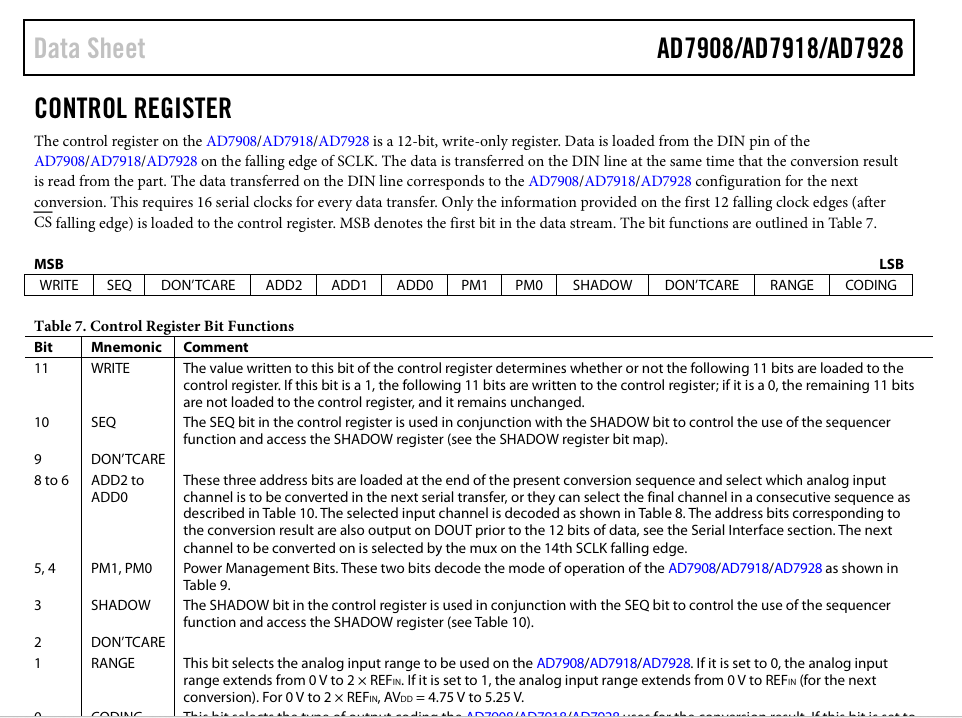

컨트롤 레지스터 제어 부분 항목.12비트 데이터 항목을 확인하자.

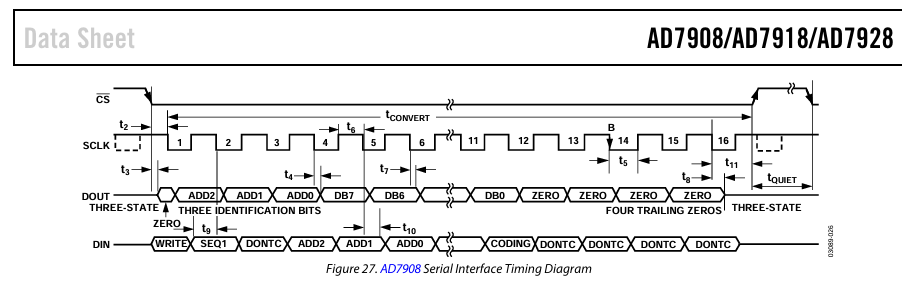

칩 셀렉(CS) 부분이 1로 유지 되었다가. low로 떨어지는 순간 클럭(sclk)을 입력 해준다. 클락이 1에서 0으로 떨어질때부터 시작한다. 각각의 16개의 클럭을 위 레지스터 부분과 비교해 끝나는 시점에 쓰기가 끝난다.

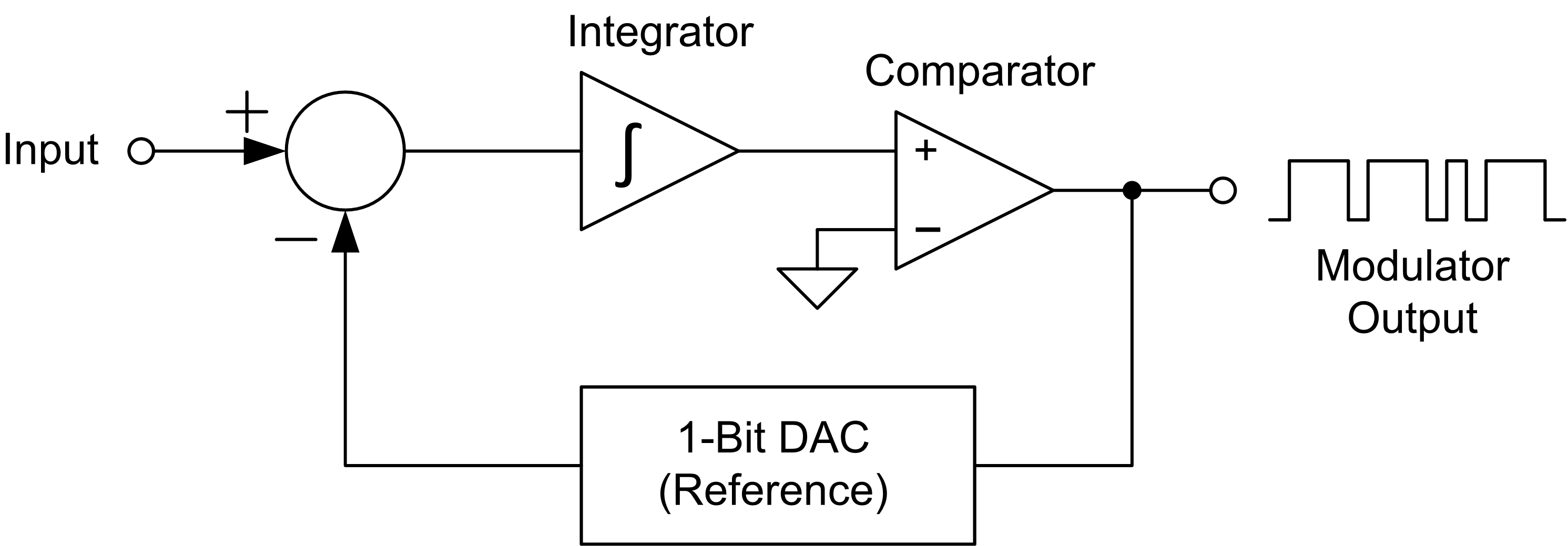

[Sigma Delta ADC] 신호의 값을 예측하여, 오차를 구한다음, 누적된 오차를 이용하여 오차를 보정해 나가는 변조 방식.

장점. 다른 ADC변환 방식보다 정밀하고 정확. 가격이 저렵하게 회로를 구성. 단점. 고속의 신호 변환이 어렵다.

적분기를 통해 오버 샘플링을 하고, 오차 보정을 해서 디지털 필터를 하는 LPF가 존재하기 때문에 정밀한 ADC라고 보면 된다. 샘플링을 여러번 하기 때문에 고속의 신호 변화가 어렵다.